User:John R. Brews/Draft

MOS Capacitor

The MOS capacitor or metal-oxide semiconductor capacitor is a two terminal device consisting of three layers: a metal gate electrode, a separating insulator (often an oxide layer), and a semiconducting layer called the body. The device operates using the field effect, that is, the modulation of the surface conductivity of the semiconductor body by means of an applied voltage between the gate and the body.

Operation

Field effect: Top panels: An applied voltage bends bands, depleting holes from surface (left). The charge inducing the bending is balanced by a layer of negative acceptor-ion charge (right). Bottom panel: A larger applied voltage further depletes holes but conduction band lowers enough in energy to populate an inversion layer.

A device based upon a uniformly doped p-type body is described. The n-type case is similar. The device has four regions of operation depending upon the applied voltage between gate and body:

- Accumulation: For a negative gate bias, holes are drawn to the semiconductor-insulator interface. A conducting surface extends from the bulk all the way to the interface, and the surface conductivity is enhanced by the accumulation of holes at the interface.

- Flat bands: For a specific value of voltage, the bulk hole density is exactly the same from the bulk to the interface. The body is everywhere charge neutral because the hole density exactly balances the acceptor density. The flatband voltage corresponds to a zero potential drop in the body, but that does not necessarily correspond to zero applied voltage because of the contact potential between the metal gate and the body that leads to band bending even when zero voltage is applied.

- Depletion: For a positive gate voltage, the holes are pushed away from the positive charge on the gate electrode, and a surface layer depleted of holes is formed extending from the interface to the depth necessary to make the exposed, immobile, negative acceptor ion charge exactly balance the positive charge on the gate. Increase in positive charge on the gate with increasing voltage is balanced by expansion of the depletion layer, increasing the acceptor charge.

- Inversion: For positive gate voltages above a threshold voltage, a surface inversion layer of electrons forms in a narrow layer near the interface. This conducting inversion layer is separated form the p-type neutral bulk by the intervening insulating depletion layer of immobile acceptor charge. Once the gate voltage increases beyond the threshold voltage, additional positive charge on the gate is compensated by increased inversion layer electron charge, and the depletion layer depth no longer expands.

These various operation regions all are subsumed under the notion of the field effect, the modulation of conductivity by an applied electric field. The figure illustrates the charge balance for the cases of depletion (top panels) and inversion (bottom panels). On the left side of the figure, the band edges are plotted as a function of depth into the capacitor. The electron population of the bands depends upon how close they are to the Fermi level (the horizontal dashed line): because this separation varies with depth, so does the occupancy of the bands. For example, the valence bands are bent far below the Fermi level near the interface, so the energy levels in the valence band near the interface are filled with electrons, and there are no holes. At greater depth from the interface, however, the valence band edge becomes the bulk value, and is close enough to the Fermi level to allow some electron vacancies (holes, in other words) in the valence band. Consequently there are holes present in the bulk region, which are of a density equal to that of the negatively charged acceptor impurities in this region, resulting in a neutral bulk. The right panels in the figure illustrate the charge densities as a function of depth that are a consequence of the band bending.

Contact potential

The flat band condition is examined further here, to explain why a zero applied voltage does not necessarily imply flat bands. The metal gate contains electrons, as does the semiconductor body. For this discussion, the insulator is imagined as a charge-free inert layer. Suppose an electron is taken from the metal and transferred to the semiconductor. There are three possibilities: no work is done, some work is done to transfer the electron, or the electron provides energy during the transfer. In the first case, zero applied voltage corresponds to flat bands, but in the other two cases a short circuit between metal and semiconductor leads to a net transfer of electrons making the gate negatively charged in the first case and the semiconductor in the second case. That is, without any applied voltage, a charge transfer occurs, and this transfer results in a potential difference at zero applied voltage, the contact potential. Thus, to achieve flat bands (zero potential drop across the semiconductor), a flatband voltage is necessary.

The underlying cause of this charge transfer at a microscopic level is complicated in detail by the effects of interfaces including interface traps, and by charges in the insulating layer related to various defects. Within a few lattice spacings of an interface (≈1nm, say), the atomic arrangement differs from the bulk materials on either side of an interface, and the chemistry associated with such distortion can lead to charge dipoles (and related potentials) near this interface, even if the junction is free from defects. Two consequences are that the band bending may depend upon the crystal orientation of the surfaces forming the interfaces, and the band bending is not dictated entirely by the behavior of the metal and semiconductor idealized as bulk media. However, the driving force at an atomic level is the ability of some atoms to strip electrons from other atoms of a different species, a phenomenon called electronegativity of the atoms.[1]

Admittance

The MOS capacitor is often used as a test structure to monitor various fabrication steps in semiconductor processing. A key to these applications is the small-signal response of this device, that is, the current that flows in a circuit connecting this device to a small-amplitude gate voltage variation superposed upon a steady bias voltage. The ratio of the alternating current to the alternating voltage is the small-signal admittance of the device, and contained in this admittance is information about interface quality (traps, for example), insulator thickness, the distribution of dopants in the semiconductor body, and information on the defects in the semiconductor itself.

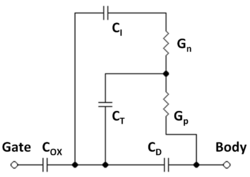

The basic ideas behind its use can be understood using the equivalent circuit in the figure. The circuit elements are:

- The oxide capacitance COX

- The depletion layer capacitance CD

- The inversion layer capacitance CI

- The trap capacitance CT

- The trap conductance for holes Gp

- The trap conductance for electrons Gn

The behavior of these various elements is described next.

Notes

- ↑ See, for example, Hisham Z Massoud (2006). “Growth kinetics and electrical properties of ultrathin silicon-dioxide layers”, Howard R. Huff, H. Iwai, H. Richter, eds: Silicon Materials Science and Technology X, Issue 2, Tenth symposium on silicon material science and technology. The Electrochemical Society, pp. 195 ff. ISBN 156677439X.